US 20150138174A1

# (19) United States

# (12) **Patent Application Publication YAMAUCHI et al.**

(10) Pub. No.: US 2015/0138174 A1

(43) **Pub. Date:** May 21, 2015

#### (54) EL DISPLAY DEVICE, DRIVING METHOD THEREOF, AND ELECTRONIC EQUIPMENT PROVIDED WITH THE EL DISPLAY DEVICE

(71) Applicant: Semiconductro Energy Laboratory Co., Ltd., Atsugi-shi (JP)

(72) Inventors: Yukio YAMAUCHI, Shimada (JP); Takeshi FUKUNAGA, Atsugi (JP)

(21) Appl. No.: 14/571,897

(22) Filed: Dec. 16, 2014

## Related U.S. Application Data

(60) Continuation of application No. 14/456,294, filed on Aug. 11, 2014, now Pat. No. 8,941,565, Continuation of application No. 14/031,088, filed on Sep. 19, 2013, now Pat. No. 8,830,146, which is a continuation of application No. 13/776,772, filed on Feb. 26, 2013, now Pat. No. 8,558,773, which is a continuation of application No. 12/892,277, filed on Sep. 28, 2010, now Pat. No. 8,405,594, which is a continuation of application No. 11/907,860, filed on Oct. 18, 2007, now Pat. No. 7,821,200, which is a continuation of application No. 10/980,600, filed on Nov. 4, 2004, now Pat. No. 7,312,572, which is a division of application No. 10/198,047, filed on Jul. 19, 2002, now Pat. No.

6,844,683, which is a division of application No. 09/599,394, filed on Jun. 21, 2000, now Pat. No. 6,452, 341.

#### (30) Foreign Application Priority Data

Jun. 21, 1999 (JP) ...... 11-174734

#### **Publication Classification**

(51) Int. Cl. G09G 3/32 (2006.01)

52) **U.S. Cl.** CPC ............. *G09G 3/3225* (2013.01); *G09G 2300/04* (2013.01); *G09G 2300/0426* (2013.01)

#### (57) ABSTRACT

An EL display device capable of performing clear multigradation color display and electronic equipment provided with the EL display device are provided, wherein gradation display is performed according to a time-division driving method in which the luminescence and non-luminescence of an EL element (109) disposed in a pixel (104) are controlled by time, and the influence by the characteristic variability of a current controlling TFT (108) is prevented. When this method is used, a data signal side driving circuit (102) and a gate signal side driving circuit (103) are formed with TFTs that use a silicon film having a peculiar crystal structure and exhibit an extremely high operation speed.

FIG. 1A

FIG. 1B

16 50 48

FIG. 3

Prior Art

FIG. 4A

FIG. 4B

550 FIG. 8B

FIG. 10

FIG. 11

613 603

605

606

607

610

614

601

FIG. 12A

FIG. 12B

FIG. 13A

FIG. 13C

FIG. 14

FIG. 16

FIG. 17

FIG. 18A

FIG. 18B

FIG. 18C

FIG. 18D

FIG. 18E

FIG. 19A

FIG. 19B

FIG. 20A

FIG. 20B

# EL DISPLAY DEVICE, DRIVING METHOD THEREOF, AND ELECTRONIC EQUIPMENT PROVIDED WITH THE EL DISPLAY DEVICE

#### BACKGROUND OF THE INVENTION

[0001] 1. Field of the Invention

[0002] This invention relates to an EL (electro-luminescence) display device formed by constructing a semiconductor device (i.e., a device made of a semiconductor thin film) on a substrate and relates to electronic equipment (electronic device) in which the EL display device is used as a display panel (display portion).

[0003] 2. Description of Related Art

[0004] In recent years, great advances have been made in a technique for forming TFTs on a substrate, and development has proceeded in the application thereof to an active matrix type display. Especially, a TFT using a polysilicon film is higher in electron field-effect mobility than a conventional TFT using an amorphous silicon film, and can operate at a high speed. Therefore, it has been made possible to control a pixel by a driving circuit formed on the same substrate on which the pixel is also formed, although the pixel had been conventionally controlled by the driving circuit disposed outside the substrate.

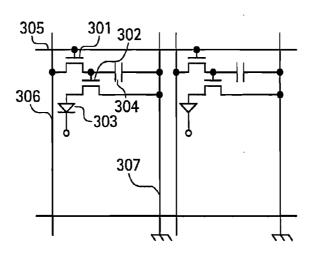

[0005] The active matrix type display is attracting public attention because it can obtain various advantages, such as reduced manufacturing costs, reduced size of the display device, increased yields, and reduced throughput, by constructing various circuits or elements on the same substrate. [0006] Conventionally, the pixel of the active matrix type EL display has been generally constructed as shown in FIG. 3. In FIG. 3, reference character 301 designates a TFT that functions as a switching element (hereinafter, referred to as switching TFT), 302 designates a TFT that functions as an element (current controlling element) to control a current supplied to an EL element 303 (hereinafter, referred to as current controlling TFT), and 304 designates a capacitor (capacitance storage). The switching TFT 301 is connected to a gate wiring line 305 and a source wiring line 306 (data wiring line). The drain of the current controlling TFT 302 is connected to the EL element 303, and the source thereof is connected to a current-feed line 307.

[0007] When the gate wiring line 305 is selected, the gate of the switching TFT 301 is opened, the data signal of the source wiring line 306 is then stored in the capacitor 304, and the gate of the current controlling TFT 302 is opened. After the gate of the switching TFT 301 is closed, the gate of the current controlling TFT 302 is kept opening by the charge stored in the capacitor 304. During that interval, the EL element 303 emits light. The amount of luminescence of the EL element 303 changes according to the amount of a flowing current.

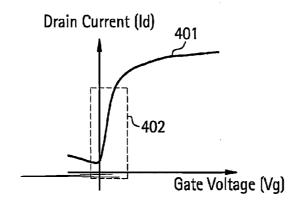

[0008] At this time, the amount of current supplied to the EL element 303 is controlled by the gate voltage of the current controlling TFT 302. This is shown in FIG. 4.

[0009] FIG. 4(A) is a graph showing transistor characteristics of the current controlling TFT. Reference character 401 is called Id-Vg characteristic (or Id-Vg curve). Herein, Id is a drain current, and Vg is a gate voltage. The amount of a flowing current corresponding to an arbitrary gate voltage can be known from this graph.

[0010] Normally, the region shown by the dotted line 402 of the Id-Vg characteristic is used when the EL element is driven. An enlarged view of the enclosed region of the dotted line 402 is shown in FIG. 4(B).

[0011] In FIG. 4(B), the region shown by the oblique lines is called a sub-threshold region. In practice, it is indicated as a region in which a gate voltage is near or less than a threshold voltage (Vth). The drain current exponentially changes according to the change of the gate voltage in this region. Using this region, the current is controlled by the gate voltage. [0012] The data signal input into a pixel by opening the switching TFT 301 is first stored in the capacitor 304, and the data signal directly acts as the gate voltage of the current controlling TFT 302. At this time, the drain current with respect to the gate voltage is determined by one-to-one according to the Id-Vg characteristic shown in FIG. 4(A). That is, a given current flows through the EL element 303 corresponding to the data signal, and the EL element 303 emits light by the amount of luminescence corresponding to the amount of the current.

[0013] The amount of luminescence of the EL element is controlled by the data signal, as mentioned above, and thereby gradation display is performed. This is a so-called analog gradation method, in which the gradation display is performed by a change in the amplitude of the signal.

[0014] However, there is a defect in that the analog gradation method is very weak in the characteristic variability of TFTs. For example, let it be assumed that the Id-Vg characteristic of a switching TFT differs from that of a switching TFT of an adjacent pixel that displays the same gradation level (i.e., a shift is performed toward a plus or a minus side overall).

[0015] In this situation, drain currents of the switching TFTs differ from each other, though depending on the level of the variability, and thus a different gate voltage will be applied to the current controlling TFT of each pixel. In other words, a different current flows through each EL element, and, as a result, a different amount of luminescence is emitted, and the display of the same gradation level cannot be achieved.

[0016] Additionally, even if an equal gate voltage is applied to the current controlling TFT of each pixel, the same drain current cannot be output if the Id-Vg characteristic of the current controlling TFTs has variability. Additionally, as is clear from FIG. 4(A), a region is used in which the drain current exponentially changes according to a change in the gate voltage, and, therefore, a situation will occur in which, if the Id-Vg characteristic shifts most slightly, the amount of current to be output becomes greatly different even if an equal gate voltage is applied thereto. If so, adjacent pixels will have a great difference in the amount of luminescence of the EL element.

[0017] In practice, each individual variability of the switching TFT and the current controlling TFT acts synergistically, and a stricter condition will be imposed. The analog gradation method is extremely sensitive to the characteristic variability of the TFTs, as mentioned above, and this has caused an obstruction to realizing the multicolor of the conventional active matrix type EL display device.

### SUMMARY OF THE INVENTION

[0018] The present invention was made in consideration of the above problem, and it is an object of the present invention to provide an active matrix type EL display device capable of performing clear multi-gradation color display. It is another object of the present invention to provide high-performance electronic equipment provided a with such an active matrix type EL display device.

[0019] The present applicant thought that a digital gradation method in which the current controlling TFT is used only as a switching element for supplying a current is better than the conventional analog gradation method in which the amount of luminescence of the EL element is controlled by controlling a current, in order to design a pixel structure to be unsusceptible to the influence of the characteristic variability of the TFT.

[0020] From this, the present applicant thought that the most desirable gradation display method in the active matrix type EL display device is a divided gradation display method, more specifically, a gradation display method under a time-division method (hereinafter, designated as time-division gradation or time-division gradation display).

**[0021]** In practice, the time-division gradation display is performed as follows. A description is herein given of a case in which the full color display of 256-gradation (16,770,000 colors) is performed according to an 8-bit digital driving method.

[0022] First of all, one frame of an image is divided into eight sub-frames. Herein, one cycle when data is input to all pixels of a displayed area is called one frame. Oscillation frequency in a normal EL display device is 60 Hz, in other words, 60 frames are formed per second. Flickering of the image, for example, begins to be visually conspicuous when the number of frames per second falls below this. A divided frame obtained by dividing one frame into a plurality of frames is called a sub-frame.

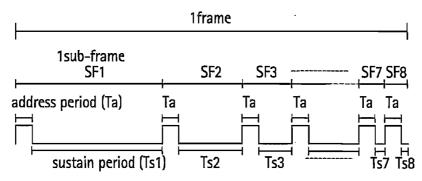

[0023] One sub-frame is divided into an address period (Ta) and a sustained period (Ts). The address period is the entire time required to input data to all pixels during one sub-frame, and the sustained period (or lighting period) is a period during which the EL element emits light. (FIG. 10)

[0024] Herein, the first sub-frame is called SF1, and the remaining sub-frames from the second to the eighth sub-frame are called SF2-SF8, respectively. The address period (Ta) is constant in SF1-SF8. On the other hand, the sustained periods (Ts) corresponding to SF1-SF8 are called Ts1-Ts8, respectively.

[0026] First of all, in a state in which a voltage is not applied (or not selected) to an opposite electrode of an EL element of a pixel (note that the opposite electrode is an electrode not connected to a TFT; normally, this is a cathode), a data signal is input to each pixel without light emission of the EL element. This period is defined as an address period. When the data is input to all the pixels and the address period is completed, a voltage is applied (or selected) to the opposite electrode, thus allowing the EL element to emit light. This period is defined as a sustained period. The period during which light is emitted (i.e., the pixel is lit) is any one of Ts1-Ts8. Let it be herein supposed that a predetermined pixel is lit during Ts8. [0027] Thereafter, taking again an address period, a data signal is input to all pixels, and then a sustained period is entered. At this time, the sustained period is any one of Ts1-Ts7. Let it be herein supposed that a predetermined pixel is lit

[0028] Thereafter, the same operation is repeated for the remaining six sub-frames, and, by setting the sequential sus-

tained periods in the order of Ts6, Ts5, . . . and Ts1, a predetermined pixel is lit in each sub-frame.

[0029] When eight sub-frames appear, one frame is finished. At this time, the gradation of the pixel is controlled by multiplying the sustained periods. For example, when Ts1 and Ts2 are selected, a brightness of 75% can be expressed on the supposition that all the light is 100%, and, when Ts3, Ts5, and Ts8 are selected, a brightness of 16% can be expressed. [0030] 256-gradation display was described above, but other gradation display can be performed.

**[0031]** When the gradation display (2"-gradation display) of n bit (n is an integer of two or more) is performed, one frame is first divided into n sub-frames (SF1, SF2, SF3, . . . SF(n-1), and SF(n)), while corresponding to the gradation of n bit. The number of divisions of one frame increases as the gradation increases, and a driving circuit must be operated at a high frequency.

[0032] The n sub-frames are each divided into address periods (Ta) and sustained periods (Ts). In other words, the address and sustained periods are selected by selecting whether to apply a voltage to an opposite electrode common to all EL elements or not.

[0033] And, the sustained period corresponding to each of the n sub-frames is processed to be Ts1:Ts2:Ts3: . . . :Ts(n-1):Ts(n)= $2^0$ : $2^{-1}$ : $2^{-2}$ : . . . : $2^{-(n-2)}$ : $2^{-(n-1)}$  (herein, the sustained period corresponding to SF1, SF2, SF3, . . . , SF(n-1), and SF(n) is Ts1, Ts2, Ts3, . . . , Ts(n-1), and Ts(n), respectively). [0034] In this state, a pixel is sequentially selected in one arbitrary frame (more strictly, the switching TFT of each pixel is selected), and a predetermined gate voltage (corresponding to a data signal) is applied to the gate electrode of the current controlling TFT. At this time, the EL element of a pixel to which the data signal actuating the current controlling TFT is input emits light only during the sustained period allocated to the sub-frame after completion of the address period. That is, a predetermined pixel emits light.

[0035] This operation is repeated in all the n sub-frames, and the gradation of each pixel is controlled by multiplying the sustained periods. Accordingly, when paying attention to an arbitrary pixel, the gradation of the pixel is controlled according to how long the pixel is lit in each sub-frame (i.e., how long the sustained period has lasted).

[0036] As mentioned above, it is the most noticeable feature of the present invention that time-division gradation display is used for the active matrix type EL display device. In order to perform this time-division gradation, one frame must be divided into a plurality of sub-frames. In other words, it is more necessary than before to improve the operating frequency of the driving circuits on the data signal side and on the gate signal side.

[0037] However, it is difficult to make a TFT capable of operating at such a high speed from the conventional polysilicon film (also called a polycrystal silicon film). The operation frequency can be decreased by dividing the driving circuit on the data signal side into a plurality of circuits, but a satisfactory result cannot be accomplished if so.

[0038] Therefore, in the present invention, use is made of a silicon film having a peculiar crystal structure in which the continuity of a grain boundary is high and the crystal orientation is unidirectional. This film is used as an active layer of a TFT, thereby allowing the TFT to exhibit very high operation and speed. That is, it is one of the features of the present invention to also perform the time-division gradation display of the active matrix type EL display device by the use of such

a high operating speed TFT. A description is hereinafter given of observed results of a silicon film used in the present invention that was made experimentally.

[0039] The silicon film used in the present invention has a crystal structure in which, microscopically, a plurality of needle-shaped crystals or bar-shaped crystals (hereinafter, designated as bar crystal) gather and form lines. This can be easily confirmed from observations according to the TEM (transmission electron microscope).

[0040] Additionally, as a result of carrying out detailed observations of an electron beam diffraction image of a spot diameter of about 1.35  $\mu$ m concerning the silicon film used in the present invention, diffraction spots corresponding to a {110} plane appear regularly in spite of the existence of a slight fluctuation, and it can be confirmed to have the {1 1 0} plane as a main orientation plane though a crystallographic axis has a slight deviation.

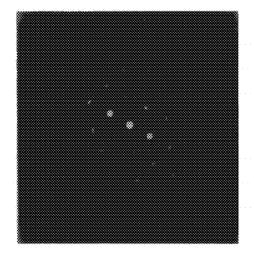

[0041] FIG. 19(A) shows an electron beam diffraction image obtained by projecting an electron beam of a spot diameter of about  $1.35 \mu m$  onto the silicon film used in the present invention. On the other hand, FIG. 19(B) shows an electron beam diffraction image obtained by projecting an electron beam onto the conventional polysilicon film under the same conditions. In each figure, the center of the photograph is a position (projected point of the electron beam) onto which the electron beam was projected.

[0042] While the diffraction spots corresponding to the  $\{1\ 1\ 0\}$  plane appear comparatively regularly in FIG. 19(A), they are arranged to be quite irregular in FIG. 19(B), and thus the orientation planes are obviously nonuniform. From this electron beam diffraction photograph, the silicon film used in the present invention can be immediately distinguished from the conventional polysilicon film.

[0043] In the electron beam diffraction image of FIG. 19(A), it is obvious, by comparison with the electron beam diffraction image of a monocrystal silicon wafer of the {110} orientation, that the diffraction spot corresponding to the {110} plane appears. Additionally, while the diffraction spot of the monocrystal silicon wafer is seen as a sharp spot, the diffraction spot of the silicon film used in the present invention has an expanse on the concentric circle centering the projected point of the electron beam.

[0044] This is also a feature of the silicon film used in the present invention. Since the  $\{1\ 1\ 0\}$  plane is an individual orientation plane for each crystal grain, it is expected that the same diffraction spot as the monocrystal silicon is obtained as far as one crystal grain is concerned. However, in practice, they exist as a collective of a plurality of crystal grains, and therefore each grain has a slight rotation around the crystal-lographic axis, and a plurality of diffraction points, each corresponding to the crystal grain appear on the concentric circle, though each crystal grain sets the  $\{1\ 1\ 0\}$  plane as its own orientation plane. The points are laid upon each other so as to exhibit an expanse.

[0045] However, since an each individual crystal grain forms a grain boundary quite excellent in consistency, as described later, the slight rotation around the crystallographic axis does not constitute a factor for ruining crystallinity. Therefore, it can be said that the electron beam diffraction image of the silicon film used in the present invention substantially has no distinction to the electron beam diffraction image of the monocrystal silicon wafer of the {1 1 0} orientation.

**[0046]** From the foregoing, it may safely be affirmed that the silicon film used as an active layer of a TFT in the present invention is the silicon film showing the electron beam diffraction image corresponding to the  $\{1\ 1\ 0\}$  orientation.

[0047] Now, a description will be given of the grain boundary of the silicon film used in the present invention. Although a description is given under the designation of "grain boundary" for convenience of explanation, this can be regarded as an interface between a certain crystal grain and another crystal grain that has derived (or branched) therefrom. Anyway, the designation of "grain boundary" including the meaning of the aforementioned interface is used in this specification.

[0048] The present applicant confirmed that, from observation of a grain boundary formed by the contact of individual bar crystals under the HR-TEM (high-resolution transmission electron microscope), there is continuity in the crystal lattice in the grain boundary. This can be easily confirmed from the fact that lattice fringes under observation are continuously linked to each other in the grain boundary.

[0049] The continuity of the crystal lattice in the grain boundary originates from the fact that it is a grain boundary called "planar boundary". The definition of the planar boundary in this specification derives from "Planar Boundary" appearing in "Characterization of High-Efficiency Cast-Si Solar Cell Wafers by MBIC Measurement; Ryuichi Shimokawa and Yutaka Hayashi, Japanese Journal of Applied Physics vol. 27, No. 5, pp. 751-758, 1988."

[0050] According to the above article, the planar boundary includes a twin grain boundary, a special lamination fault, and a special twist grain boundary. This planar boundary has a feature in that it is electrically inert. That is, although it is a grain boundary since the planar boundary does not function as a trap to obstruct the movement of a carrier, it can in fact be considered as no existence.

[0051] Especially, when the crystallographic axis (axis perpendicular to the crystal plane) is the <110> axis, the {211} twin grain boundary and the {111} twin grain boundary are often called a corresponding grain boundary of  $\Sigma$ 3. A  $\Sigma$  value is a parameter serving as an indicator that shows the level of the consistency of the corresponding grain boundary, and it is known that the grain boundary increases in excellence in consistency as the  $\Sigma$  value falls.

[0052] As a result of observing the silicon film used in the present invention by the TEM, almost all the grain boundaries have proved to be corresponding grain boundaries of  $\Sigma 3$ . This was judged from the fact that a grain boundary formed between two crystal grains becomes the corresponding grain boundary of  $\Sigma 3$  when  $\theta = 70.5^{\circ}$  wherein  $\theta$  is an angle formed by the lattice fringes corresponding to the  $\{111\}$  plane when the plane orientation of both crystal grains is  $\{1\ 1\ 0\}$ .

[0053] It is noted that it becomes the corresponding grain boundary of  $\Sigma 9$  when  $\theta$ =38.9°, and other grain boundaries, such as this grain boundary, also exist.

[0054] The crystal structure (more accurately, structure of the grain boundary) shows that two crystal grains different in the grain boundary are connected to each other with quite excellently consistency. In other words, a structure is established in which crystal lattices range continuously in the grain boundary, and it is very difficult to create a trap level resulting from, for example, a crystal fault Therefore, a semiconductor thin film that has a crystal structure such as the above One can in fact be considered to have no grain boundary.

[0055] It is confirmed by TEM observation that faults (stacking fault etc.) existing in the crystal grain disappear

almost completely by conducting a heating process at 700-1150° C. in sequential steps when the silicon film used in the present invention is formed. This is apparent from the fact that the number of faults is greatly decreased before and after the heating process.

[0056] The difference in the number of faults appears as the difference in the spin density according to electron spin resonance analysis (ESR analysis). In the current state, the spin density of the silicon film used in the present invention has proved to be at least  $5 \times 10^{17}$  spins/cm<sup>3</sup> or less (preferably,  $3 \times 10^{17}$  spins/cm<sup>3</sup> or less). However, since this measurement value is close to the detection limit of measuring devices in existence, it is expected that an actual spin density is even lower.

[0057] A further detailed description of the silicon film used in the present invention can be supplied by Patent Application Nos. 044659 of 1998, 152316 of 1998, 152308 of 1998, and 152305 of 1998, each filed by the present applicant. [0058] A TFT in which the silicon film used in the present invention is experimentally made an active layer shows an electrical characteristic that equals MOSFET. The following data are obtained from the TFT (in which the film thickness of the active layer is 30 nm, and that of the gate insulating film is 100 nm) experimentally made by the present applicant.

[0059] (1) The sub-threshold coefficient which is the index of switching performance (quickness of on/off operation switch) is 60~100 mV/decade (representatively, 60~85 mV/decade) in both N-channel type TFT and P-channel type TFT: this value is small.

[0060] (2) The electron field-effect mobility ( $\mu_{FE}$ ) which is the index of the operation speed of the TFT is 200~650 cm²/Vs (300~500 cm²/Vs representatively) in N-channel type TFT, and is 100~300 cm²/Vs (150~200 cm²/Vs representatively) in P-channel type TFT: these values are large.

**[0061]** (3) The threshold voltage ( $V_{th}$ ) which is the index of the driving voltage of the TFT is  $-0.5\sim1.5$  in N-channel type TFT, and is  $-1.5\sim0.5$  in P-channel type TFT: these values are small.

[0062] It is confirmed to be capable of realizing quite excellent switching characteristics and high-speed operation properties, as described above. In addition, in a ring oscillator experimentally made by the use of the TFT, the oscillation frequency of about 1 GHz is obtained at the maximum. The ring oscillator is constructed as follows.

[0063] Number of steps: nine steps;

[0064] Film thickness of the gate insulating film of the TFT: 30 nm and 50 nm;

[0065] Gate length of the TFT (channel-length): 0.6  $\mu m$ .

[0066] Additionally, as a result of actually making a shift register experimentally and confirming the operation frequency, the output pulse of the operation frequency of 100 MHz is obtained in the shift register in which the film thickness of the gate insulating film is 30 nm, the gate length is 0.6  $\mu$ m, the power supply voltage is 5V, and the number of steps is 50.

[0067] The marvelous data of the ring oscillator and the shift register mentioned above indicate that the TFT in which the silicon film used in the present invention is made an active layer equals MOSFET, which uses a monocrystal silicon, or has operational performance surpassing MOSFET.

#### BRIEF DESCRIPTION OF THE DRAWINGS

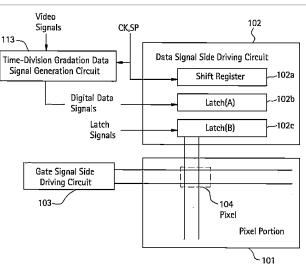

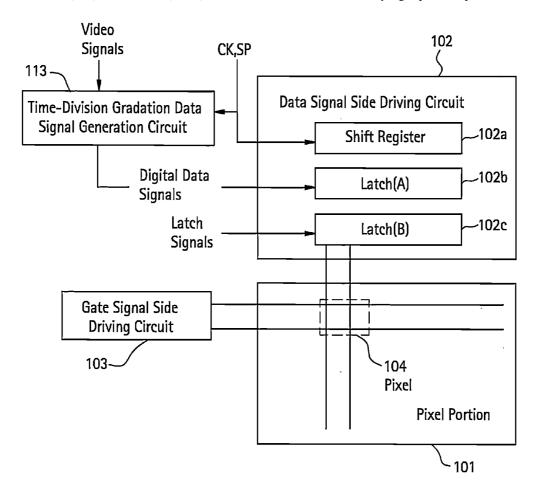

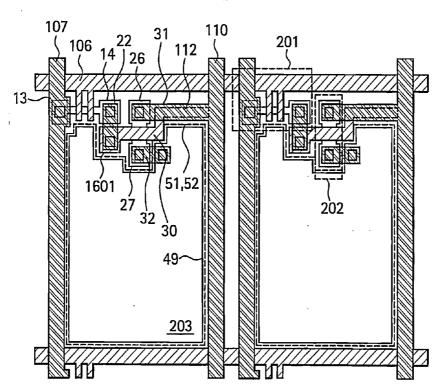

[0068] FIGS. 1A and 1B show structures of an EL display device.

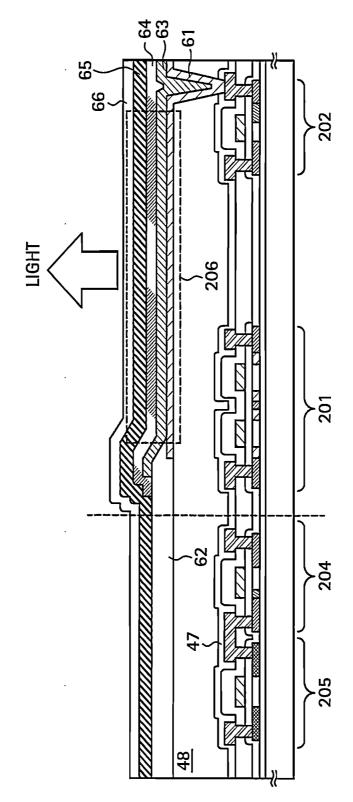

[0069] FIG. 2 shows a sectional structure of the EL display device.

[0070] FIG. 3 shows a structure of a pixel portion of a conventional EL display device.

[0071] FIGS. 4A and 4B are views explaining TFT characteristics used in an analog gradation method.

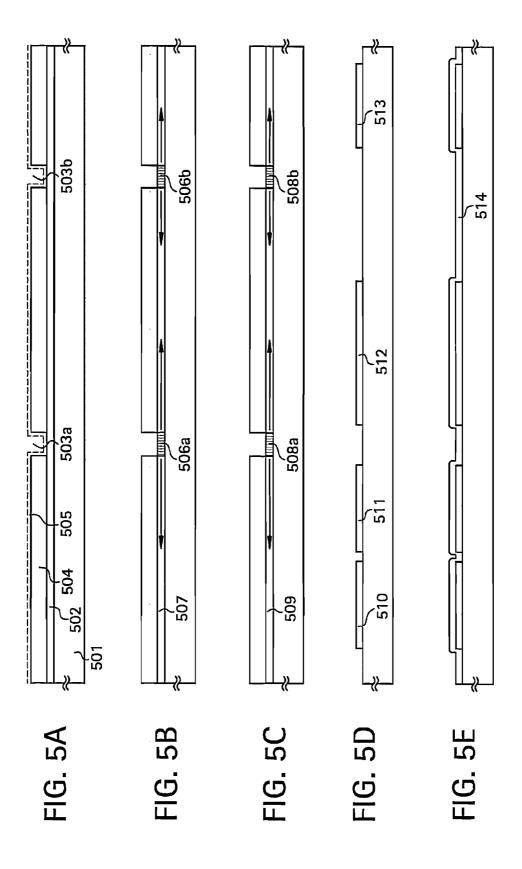

[0072] FIGS. 5A-5E show manufacturing steps of the EL display device.

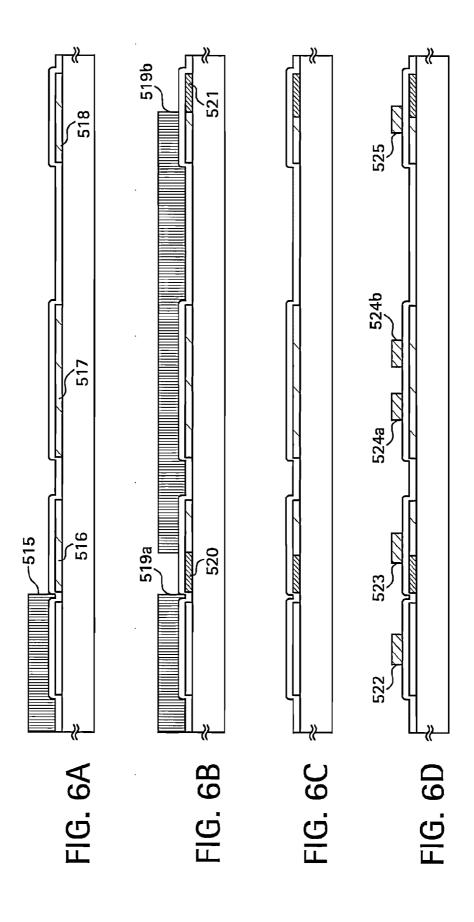

[0073] FIGS. 6A-6D show manufacturing steps of the EL display device.

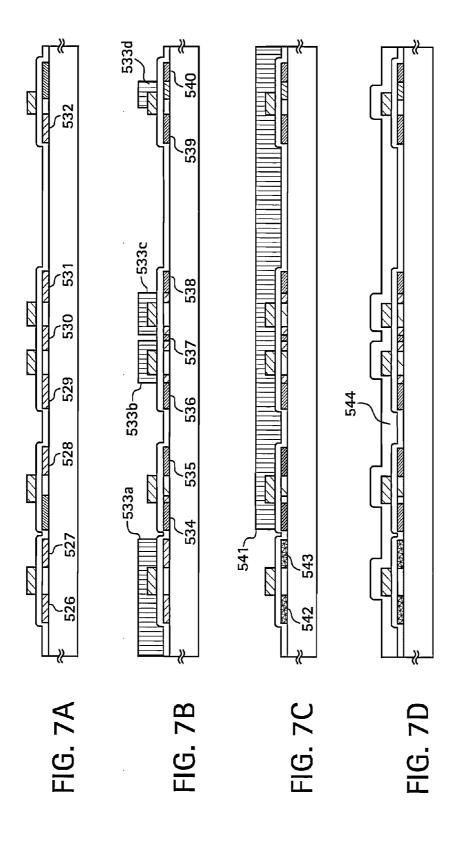

[0074] FIGS. 7A-7D show manufacturing steps of the EL display device.

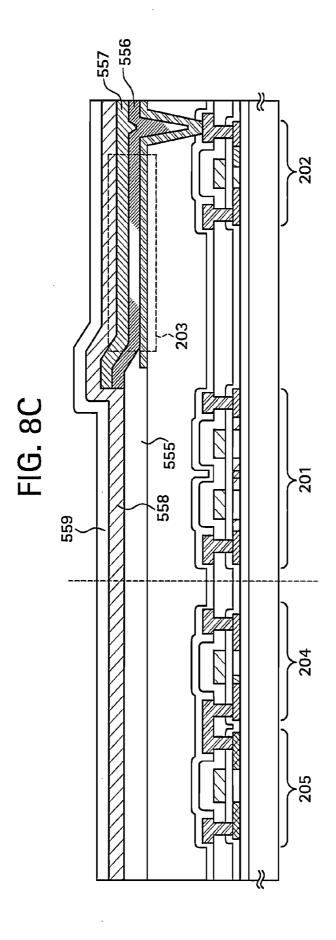

[0075] FIGS. 8A-8C shows manufacturing steps of the EL display device.

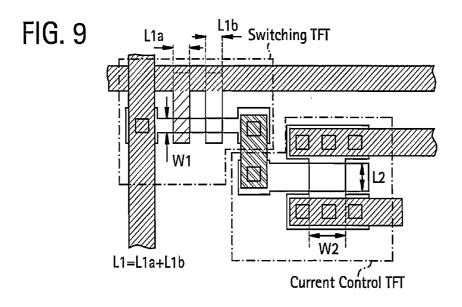

[0076] FIG. 9 is an enlarged view of the pixel portion of the EL display device.

[0077] FIG. 10 is a view explaining the operation mode of a time-division gradation method.

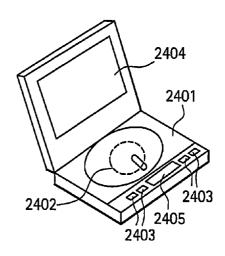

[0078] FIG. 11 shows an external appearance of an EL module.

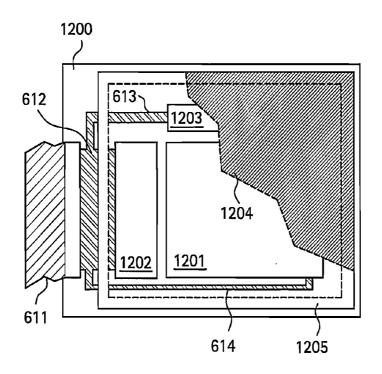

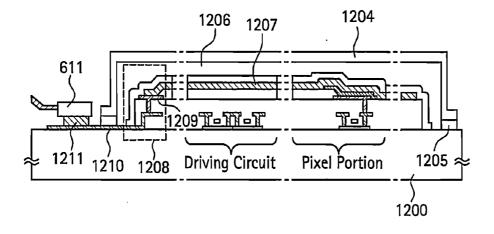

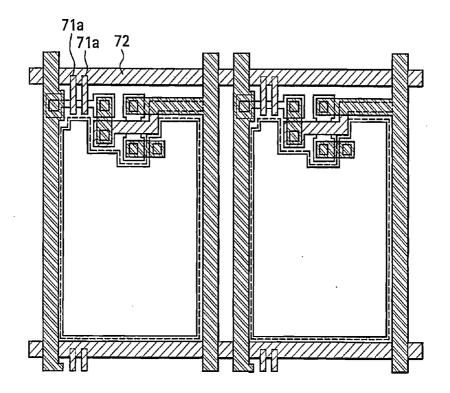

[0079] FIGS. 12A and 12B show external appearances of the EL module.

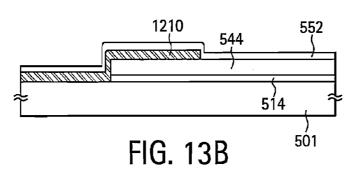

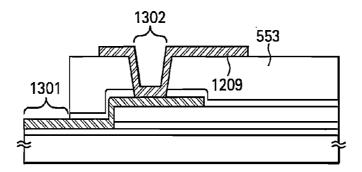

[0080] FIGS. 13A-13C show manufacturing steps of a contact structure.

[0081] FIG. 14 shows a structure of the pixel portion of the EL display device.

[0082] FIG. 15 shows a sectional structure of the EL display device.

[0083] FIG. 16 shows an upper face structure of the pixel portion of the EL display device.

[0084] FIG. 17 shows an upper face structure of the pixel portion of the EL display device.

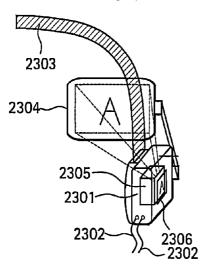

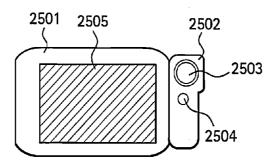

[0085] FIGS. 18A-18E show concrete examples of the electronic equipment.

[0086] FIGS. 19A and 19B are photographs substituted for a drawing, showing an electron beam diffraction image of a polysilicon film.

[0087] FIGS. 20A and 20B are a photographs substituted for a drawing, showing an example of display images of the EL display device of the present invention.

# DETAILED DESCRIPTION OF THE PREFERRED EMBODIMENTS

[0088] First, the circuit structure of the active matrix type EL display device of the present invention is shown in FIG. 1(A). In the active matrix type EL display device of FIG. 1(A), a pixel portion 101, a data signal side driving circuit 102, and a gate signal side driving circuit 103 disposed around the pixel portion are formed by TFTs formed on a substrate. Instead, the data side signal side driving circuit and the gate signal side driving circuit may be disposed, with the pixel portion therebetween, in the form of a pair of circuits.

[0089] The data signal side driving circuit 102 basically includes a shift register 102a, a latch(A) 102b, and a latch(B) 102c. Clock pulses (CK) and start pulses (SP) are input to the shift register 102a, digital data signals are input to the latch (A) 102b, and latch signals are input to the latch(B) 102c.

[0090] In the present invention, the data signal input to the pixel portion 101 is a digital signal, and voltage gradation display is not performed although it is done in a liquid crystal display device. Thus, the digital data signal that has information of 0" or "1" is input to the pixel portion 101 directly.

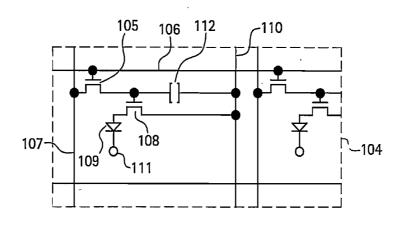

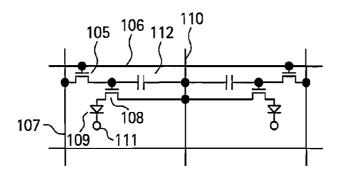

[0091] A plurality of pixels 104 are arranged in the pixel portion 101 like a matrix. An enlarged view of a pixel 104 is

shown in FIG. 1(B). In FIG. 1(B), reference numeral 105 is a switching TFT. This is connected to a gate wiring line 106 for inputting gate signals, and a data wiring line 107 (also called a source wiring line) for inputting data signals.

[0092] Reference numeral 108 is a current controlling TFT. The gate thereof is connected to the drain of the switching TFT 105. The drain of the current controlling TFT 108 is connected to an EL element 109, and the source thereof is connected to a current-feed line 110. The EL element 109 is made up of an anode (pixel electrode) connected to the current controlling TFT 108 and a cathode (opposite electrode) facing the anode, with an EL layer between the anode and the cathode. The cathode is connected to a given power line 111. [0093] When the switching TFT 105 is in a non-selective state (off state), a capacitor 112 is provided to maintain a gate voltage of the current controlling TFT 108. The capacitor 112 is connected to the drain of the switching TFT 105 and to the current-feed line 110.

[0094] The digital data signal input to the pixel portion as mentioned above is generated by a time-division gradation data signal generation circuit 113. The circuit 113 is to convert a video signal (including image information) that is comprised of analog signals or digital signals into a digital data signal for performing time-division gradation and, in addition, to generate timing pulses, etc., required to performing time-division gradation display.

**[0095]** Typically, the time-division gradation data signal generation circuit **113** includes a means for dividing one frame into n sub-frames corresponding to the gradation of n bit (n is an integer of two or more), a means for selecting an address period and a sustained period in the n sub-frames, and a means for setting the sustained period to be Ts1:Ts2:Ts3: . . .:Ts(n-1):Ts(n)= $2^{0}$ : $2^{-1}$ : $2^{-2}$ :. . . : $2^{-(n-2)}$ : $2^{-(n-1)}$ .

[0096] The time-division gradation data signal generation circuit 113 can be disposed outside the EL display device of the present invention. If so, digital data signals generated at that place are input to the EL display device of the present invention. In this case, electronic equipment that has the EL display device of the present invention as a display panel will include the EL display device and the time-division gradation data signal generation circuit of the present invention as different constituents.

[0097] Additionally, the time-division gradation data signal generation circuit 113 can be mounted on the EL display device of the present invention in the form of for example, an IC chip. If so, digital data signals generated in the IC chip are input to the EL display device of the present invention. In this case, electronic equipment that has the EL display device of the present invention as a display panel will include the EL display device of the present invention on which the IC chip including the time-division gradation data signal generation circuit is mounted as a constituent.

[0098] Finally, the time-division gradation data signal generation circuit 113 can be constructed by TFTs disposed on the same substrate as the pixel portion 104, the data signal side driving circuit 102, and the gate signal side driving circuit. If so, all can be processed on the substrate when video signals including image information are input to the EL display device. In this case, it is preferable to construct the time-division gradation data signal generation circuit by TFTs in which, as mentioned above, the silicon film used in the present invention is made into an active layer, of course. Additionally, in this case, electronic equipment that has the EL display device of the present invention as a display panel

is constructed such that the time-division gradation data signal generation circuit is built in the EL display device itself. Thus, the electronic equipment can be made more compact. [0099] Next, reference is made to FIG. 2 schematically showing the sectional structure of the active matrix type EL

display device of the present invention.

[0100] In FIG. 2, reference numeral 11 is a substrate, and 12 is an insulating film that is a base (hereinafter, this film is designated as base film). For the substrate 11, use can be made of a light transmissible substrate, representatively, a glass substrate, a quartz substrate, a glass ceramic substrate, or a crystallization glass substrate. However, it must be resistible to the highest processing temperature in a manufacturing

[0101] The base film 12 is effective especially in using a substrate that has a movable ion or a substrate that has conductivity, but it is not necessarily disposed on the quartz substrate. An insulating film that contains silicon can be used as the base film 12. It should be noted that, in this specification, "insulating film that contains silicon" signifies an insulating film in which oxygen or nitrogen is added to silicon at a predetermined ratio (SiOxNy: x and y are arbitrary integers), such as a silicon oxide film, a silicon nitride film or a silicon nitride oxide film.

[0102] Reference numeral 201 is a switching TFT, and 202 is a current controlling TFT. Both of them are formed by an n-channel type TFT. Since the electron field-effect mobility of the n-channel type TFT is larger than that of the p-channel type TFT, the n-channel type TFT can work at a higher operation speed and allow a heavy-current to flow easily. Concerning the size of the TFT required when the same amount of current is passed, the n-channel type TFT is smaller. Therefore, it is desirable to use the n-channel type TFT as the current controlling TFT because the effective luminescence area of an image display panel is widened.

[0103] However, in the present invention, there is no need to limit the switching TFT and the current controlling TFT to the n-channel type TFT. It is also possible to use the p-channel type TFT for both of them or any one thereof.

[0104] The switching TFT 201 is made up of an active layer that includes a source region 13, a drain region 14, LDD regions 15a-15d, an isolation region 16, and channel formation regions 17a, 17b, a gate insulating film 18, gate electrodes 19a, 19b, a 1st interlayer insulating film 20, a source wiring line 21, and a drain wiring line 22. The gate insulating film 18 or the 1st interlayer insulating film 20 can be common to all TFTs on the substrate, or can be varied according to circuits or elements.

[0105] In the switching TFT 201 shown in FIG. 2, the gate electrodes 19a, 19b are connected electrically, in other words, a so-called double gate structure is established. Not only the double gate structure but also a so-called multi gate structure, such as a triple gate structure, can be established, of course. The multi gate structure signifies a structure including an active layer that has two channel formation regions or more connected in series.

[0106] The multi gate structure is very effective to decrease an OFF-state current, and if the OFF-state current of the switching TFT is decreased sufficiently, the capacity necessary for the capacitor 112 shown in FIG. 1(B) can be reduced. That is, since the possession area of the capacitor 112 can be reduced, the multi gate structure is also effective to widen the effective luminescence area of the EL element 109.

[0107] In the switching TFT 201, the LDD regions 15a-15d are disposed not to overlap with the gate electrodes 19a and 19b, with the gate insulating film 18 therebetween. The thus built structure is very effective to decrease the OFF-state current. The length (width) of the LDD regions 15a-15d is  $0.5-3.5 \, \mu m$ , representatively,  $2.0-2.5 \, \mu m$ .

[0108] It is more desirable to form an offset region (i.e., region formed with a semiconductor layer whose composition is the same as the channel formation region, and in which a gate voltage is not applied) between the channel formation region and the LDD region, in order to decrease the OFF-state current. In the multi gate structure that has two gate electrodes or more, the isolation region 16 (i.e., region whose concentration is the same and to which the same impurity element is added as the source region or the drain region) formed between the channel formation regions is effective to decrease the OFF-state current.

[0109] The current controlling TFT 202 is made up of an active layer that includes a source region 26, a drain region 27, an LDD region 28, and a channel formation region 29, a gate insulating film 18, a gate electrode 30, the 1st interlayer insulating film 20, a source wiring line 31, and a drain wiring line 32. The gate electrode 30 can be a multi gate structure instead of the single gate structure.

[0110] The drain of the switching TFT is connected to the gate of the current controlling TFT, as shown in FIG. 1(B). In more detail, the gate electrode 30 of the current controlling TFT 202 is connected electrically to the drain region 14 of the switching TFT 201 through the drain wiring line 22 (also called connection wiring line). The source wiring line 31 is connected to the current-feed line 110 of FIG. 1(B).

[0111] The current controlling TFT 202 is an element to control the amount of current supplied to the EL element, and a comparatively large amount of current can flow therethrough. Therefore, preferably, the channel-width (W) is designed to be greater than the channel-width of the switching TFT. Additionally, preferably, the channel-length (L) is designed to be long so that an excessive current does not flow through the current controlling TFT 202. A desirable value is  $0.5-2 \,\mu\text{A}$  ( $1-1.5 \,\mu\text{A}$  preferably) per pixel.

[0112] From the foregoing, preferably, W1 is 0.1-5  $\mu m$  (1-3  $\mu m$  representatively), W2 is 0.5-30  $\mu m$  (2-10  $\mu m$  representatively), L1 is 0.2-18  $\mu m$  (2-15  $\mu m$  representatively), and L2 is 0.1-50  $\mu m$  (1-20  $\mu m$  representatively), wherein L1 is the channel-length of the switching TFT (L1=L1a+L1b), W1 is the channel-width thereof, L2 is the channel-length of the current controlling TFT, and W2 is the channel-width thereof, as shown in FIG. 9.

[0113] The EL display device shown in FIG. 2 also has a feature in that, in the current controlling TFT 202, the LDD region 28 is formed between the drain region 27 and the channel formation region 29, and, in addition, the LDD region 28 has a region overlapping with the gate electrode 30 and a region not overlapping therewith, with the gate insulating film 18 between the LDD region 28 and the gate electrode 30

[0114] The current controlling TFT 202 passes a relatively large amount of current so that the EL element 203 emits light, and it is desirable to devise a countermeasure for deterioration caused by injection of a hot carrier. The current controlling TFT 202 is kept in an off state when a black color is displayed. In that situation, a attractive black color cannot be displayed if the OFF-state current is high, and a fall in

contrast, for example, is brought about. Therefore, it is necessary to suppress the OFF-state current also.

[0115] Concerning the deterioration by the injection of the hot carrier, it is known that the structure in which the LDD region overlaps with the gate electrode is very effective. However, since the OFF-state current increases if the whole of the LDD region is caused to coincide therewith, the present applicant has solved the problem of countermeasures against both the hot carrier and the OFF-state current at the same time by providing a new structure in which the LDD region that is not coincident with the gate electrode is disposed in series, in addition to the aforementioned structure.

[0116] At this time, the length of the LDD region that overlaps with the gate electrode is designed to be 0.1-3  $\mu$ m (0.3-1.5  $\mu$ m preferably). The parasitic capacitance will be enlarged if it is too long, and the effect to prevent the hot carrier will be weakened if it is too short. The length of the LDD region that does not overlap with the gate electrode is designed to be 1.0-3.5  $\mu$ m (1.5-2.0  $\mu$ m preferably). A sufficient current cannot be passed if it is too long, and the effect to decrease the OFF-state current will be weakened if it is too short.

[0117] Since the parasitic capacitance is formed in the region where the gate electrode and the LDD region overlap with each other in the above structure, it is desirable to not dispose it between the source region 26 and the channel formation region 29. All that is required is to dispose the LDD region only on the drain region side because the flowing direction of the carrier (herein, electrons) in the current controlling TFT is always the same.

[0118] From the viewpoint of increasing the amount of current to be passed, it is also effective to thicken the film thickness of the active layer (specifically, the channel formation region) of the current controlling TFT 202 (50-100 nm preferably, and 60-80 nm further preferably). On the other hand, from the viewpoint of decreasing the OFF-state current in the switching TFT 201, it is also effective to thin the film thickness of the active layer (specifically, the channel formation region) (20-50 nm preferably, and 25-40 nm further preferably).

[0119] The structure of the TFT formed in the pixel was described above. In this formation, a driving circuit is also formed at the same time. A CMOS circuit that is a base unit to form the driving circuit is shown in FIG. 2.

[0120] In FIG. 2, a TFT that has a structure to decrease the hot carrier injection without reducing the operation speed to the utmost is used as the n-channel type TFT 204 of the CMOS circuit. The driving circuit described herein is the data signal side driving circuit 102 and the gate signal side driving circuit 103, each shown in FIG. 1. It is also possible to form other logic circuits (level shifter, A/D converter, signal division circuit, etc.), of course.

[0121] The active layer of the n-channel type TFT 204 includes a source region 35, a drain region 36, an LDD region 37, and a channel formation region 38. The LDD region 37 overlaps with the gate electrode 39, with the gate insulating film 18 therebetween.

**[0122]** The reason for forming the LDD region only on the drain region side is not to reduce the operation speed. There is no need to worry about the OFF-state current value in the n-channel type TFT **204**. Instead, the operation speed should be rated above it. Therefore, preferably, the LDD region **37** is

completely laid on the gate electrode, thus reducing a resistance component as much as possible. That is, a so-called offset should be omitted.

[0123] In the p-channel type TFT 205 of the CMOS circuit, there is no need to provide the LDD region especially because the deterioration caused by the hot carrier injection is quite negligible. Therefore, the active layer includes a source region 40, a drain region 41, and a channel formation region 42. The gate insulating film 18 and the gate electrode 43 are disposed thereon. It is also possible to dispose the LDD region as well as the n-channel type TFT 204 in order to take countermeasures against the hot carrier, of course.

[0124] When a p-channel type TFT is used as the current controlling TFT 202, it can have the same structure as the p-channel type TFT 205.

[0125] The n-channel type TFT 204 and the p-channel type TFT 205 are covered with the first interlayer insulating film 20, and the source wiring lines 44, 45 are formed. The two are connected electrically by the drain wiring line 46.

[0126] Reference numeral 47 is a first passivation film. The film thickness thereof is 10 nm-1  $\mu m$  (200-500 nm preferably). An insulating film including silicon (especially, a silicon nitride oxide film or a silicon nitride film is desirable) can be used as its material. The passivation film 47 serves to protect a formed TFT from alkali metal and water. The EL layer finally disposed above the TFT includes alkali metal such as sodium. In other words, the first passivation film 47 serves also as a protective layer by which the alkali metal (movable ions) is not allowed to enter the TFT side.

[0127] Reference numeral 48 is a second interlayer insulating film, and serves as a flattening film to flatten level differences formed by the TFT. Preferably, an organic resin film, such as polyimide, polyamide, acrylic resin, or BCB (benzocyclobutene) is used as the second interlayer insulating film 48. These films have an advantage in that a good smooth plane can be easily formed, and the dielectric constant is low. It is preferable to entirely absorb the level difference caused by the TFT by means of the second interlayer insulating film because the EL layer is very sensitive to ruggedness. Additionally, it is preferable to form a low-dielectric constant material thick, in order to decrease the parasitic capacitance formed between the gate wiring line or the data wiring line and the cathode of the EL element. Therefore, preferably, the film thickness thereof is 0.5-5 µm (1.5-2.5 µm preferably).

[0128] Reference numeral 49 is a pixel electrode (anode of the EL element) that is made of a transparent conductive film. After a contact hole (opening) is made in the second interlayer insulating film 48 and the first passivation film 47, the electrode is connected to the drain wiring line 32 of the current controlling TFT 202 through the opening. When the pixel electrode 49 and the drain region 27 are arranged not to be connected directly, as in FIG. 2, the alkali metal of the EL layer can be prevented from entering the active layer via the pixel electrode.

[0129] A third interlayer insulating film 50 whose thickness is 0.3-1  $\mu$ m is disposed on the pixel electrode 49. The film 50 is made of a silicon oxide film, a silicon nitride oxide film, or an organic resin film. The third interlayer insulating film 50 is provided with an opening on the pixel electrode 49 by etching, and the edge of the opening is etched to have a taper shape. Preferably, the angle of the taper is 10-60° (30-50° preferably).

[0130] An EL layer 51 is formed on the third interlayer insulating film 50. The EL layer 51 is used in the form of a

single-layer structure or a layered structure. The layered structure is superior in luminous efficiency. Generally, a positive hole injection layer/a positive hole transporting layer/a luminescent layer/an electronic transporting layer are formed on the pixel electrode in this order. Instead, a structure may be used which has the order of positive hole transporting layer/luminescent layer/electronic transporting layer or the order of positive hole injection layer/positive hole transporting layer/luminescent layer/electronic transporting layer/electronic injection layer. In the present invention, any one of the known structures can be used, and fluorescent coloring matter, etc., can be doped to the EL layer.

[0131] For example, materials indicated in the following U.S. patents or publications can be used as the organic EL material; U.S. Pat. Nos. 4,356,429: 4,539,507: 4,720,432: 4,769,292: 4,885,211: 4,950,950: 5,059,861: 5,047,687: 5,073,446: 5,059,862: 5,061,617: 5,151,629: 5,294,869: 5,294,870, and Japanese Laid-Open Patent Publication Nos. 189525 of 1998: 241048 of 1996: 78159 of 1996, and Photochemical Processes in Organized Molecular Systems pp. 437-450 "Electroluminescence in Organic Thin Films", Tetsuo Tsutsui et al.

**[0132]** The EL display device mainly has four color display methods; method of forming three kinds of EL elements that correspond to R (red), G (green), and B (blue), respectively method of combining an EL element of white luminescence and a color filter (coloring layer): method of combining an EL element of blue or blue-green luminescence and a fluorescent body (fluorescent color conversion layer: CCM): and method of stacking the EL elements that correspond to RGB while using a transparent electrode for a cathode (opposite electrode).

[0133] The structure of FIG. 2 is an example in which the method of forming three kinds of EL elements that correspond to RGB is used. Only one pixel is shown in FIG. 2. In fact, pixels, each having the same structure, are formed to correspond to each color of red, green, and blue, and thereby color display can be performed.

[0134] The present invention can be performed regardless of the luminescence method, and can use all the four methods. However, since the speed of response of the fluorescent body is slower than that of the EL, and the problem of afterglow occurs, the method in which the fluorescent body is not used is preferable. Additionally, it can be said that a color filter that causes the fall of luminescence brightness should not be used if possible.

[0135] A cathode 52 of the EL element is disposed on the EL layer 51. A material that includes magnesium (Mg), lithium (Li) or calcium (Ca) that is small in work function is used as the cathode 52. Preferably, use is made of an electrode made of MgAg (material in which Mg and Ag are mixed in the ratio of Mg:Ag=10:1). Instead, a MgAgAl electrode, a LiAl electrode, or LiFAl electrode can be used.

[0136] It is preferable to form the cathode 52 continuously without air exposure after the EL layer 51 is formed. The reason is that an interface state between the cathode 52 and the EL layer 51 greatly influences the luminous efficiency of the EL element. In this specification, the luminescence element formed by the pixel electrode (anode), the EL layer, and the cathode is called an EL element.

[0137] It is necessary to form a layered body comprised of the EL layer 51 and the cathode 52 by each pixel individually. However, the EL layer 51 is quite weak to water, and a normal photolithography technique cannot be used. Therefore, it is

preferable to use a physical mask material, such as metal mask, and selectively form it according to a vapor phase method, such as a vacuum deposition method, a sputtering method, or a plasma CVD method.

[0138] It is also possible to use an ink jet method, a screen printing method, and the like, as the method of selectively forming the EL layer. However, these methods cannot continuously form the cathode in the current state of the art, and it can be said that the method described above, not the ink jet method, etc., is desirable.

[0139] Reference numeral 53 is a protective electrode. This is to protect the cathode 52 from outside water, etc., and, at the same time, connect the cathode 52 of each pixel. For the protective electrode 53, it is preferable to use a low-resistance material including aluminum (Al), copper (Cu), or silver (Ag). A cooling effect to lower the heat of the EL layer can be expected from the protective electrode 53. It is also effective to continue to the protective electrode 53 without air exposure after the EL layer 51 and the cathode 52 are formed.

[0140] Reference numeral 54 is a second passivation film, and, preferably, the film thickness thereof is 10 nm-1 µm (200-500 nm preferably). A main purpose to dispose the second passivation film 54 is to protect the EL layer 51 from water. It is also effective to give it a cooling effect. However, the EL layer is weak to heat as mentioned above, and film formation should be performed at a low temperature (ranging from a room temperature to 120° C. preferably). Therefore, it can be said that a desirable film formation method is the plasma CVD method, sputtering method, vacuum deposition method, ion plating method, or solution application method (spin coating method).

[0141] Needless to say, all the TFTs shown in FIG. 2 have the silicon films used in the present invention as active layers. [0142] One of the purports of the present invention is to form TFTs that show a high operation speed by using a silicon film that has a peculiar crystal structure in which the continuity of the grain boundary is high as an active layer of the TFT and the crystal orientation is uniform, and, accordingly, perform time-division gradation display of an active matrix type EL display device integral with a driving circuit. Therefore, the present invention is not limited to the structure of the EL display device of FIG. 2, which is just one of the preferred embodiments.

[0143] The TFT that uses the silicon film used in the present invention can show a high operation speed, and is therefore apt to undergo deterioration caused by, for example, hot carrier injection. Therefore, as shown in FIG. 2, it is very effective to form TFTs (a switching TFT low sufficiently in OFF-state current and a current controlling TFT strong in hot carrier injection) having different structures according to a function in pixels, in order to manufacture an EL display device that has high reliability and can perform excellent image display (i.e., can show high operational performance).

#### Embodiment 1

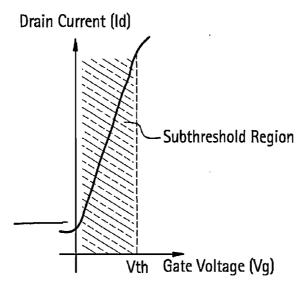

[0144] An embodiment of the present invention will be described with reference to FIGS. 5 to 8. A description is here given of a method of simultaneously manufacturing TFTs of a pixel portion and a driving circuit portion around the pixel portion. Concerning the driving circuit, a CMOS circuit that is a base unit is shown in the figure, for a brief description.

[0145] First, a substrate 501 in which a base film (not shown) is disposed on the surface thereof is prepared as

shown in FIG. 5(A). In this embodiment, a silicon nitride

oxide film whose thickness is 200 nm and another silicon nitride oxide film whose thickness is 100 nm are laminated and are used as a base film on a crystallization glass. At this time, preferably, the concentration of nitrogen of the film contacting the crystallization glass substrate is kept to 10-25 wt %. It is possible to form an element directly on the quartz substrate without any base film, of course.

[0146] Thereafter, an amorphous silicon film 502 whose thickness is 45 nm is formed on the substrate 501 by a well-known film formation method. There is no need to limit it to the amorphous silicon film. Instead, a semiconductor film (including a microcrystal semiconductor film) that has an amorphous structure can be used in this embodiment. A compound semiconductor film that has an amorphous structure, such as an amorphous silicon germanium film, also can be used herein.

[0147] Concerning the steps from here to FIG. 5(C), it is possible to completely cite Japanese Laid-open Patent Publication No. 247735 of 1998 filed by the present applicant. This publication discloses a technique concerning a method of crystallizing a semiconductor film, which uses an element, such as Ni, as a catalyst.

[0148] First, a protective film 504 that has openings 503a and 503b is formed. A silicon oxide film 150 nm thick is used in this embodiment A layer 505 that contains nickel (Ni) is formed on the protective film 504 by a spin court method. Concerning the formation of the Ni containing layer, reference can be made to the above publication.

[0149] Thereafter, as shown in FIG. 5(B), heating processing at 570° C. for 14 hours is performed in an inert atmosphere, and the amorphous silicon film 502 is crystallized. At this time, crystallization progresses substantially in parallel with the substrate, starting from regions 506a and 506b (hereinafter, designated as Ni addition region) with which Ni is in contact. As a result, a polysilicon film 507 is formed that has a crystal structure in which bar crystals gather and form lines. It is known that diffraction spots corresponding to the  $\{1\ 1\ 0\}$  orientation as shown in FIG. 19(A) are observed in an electron beam diffraction photograph at this stage.

[0150] Thereafter, as shown in FIG. 5(C), an element (phosphorus preferably) that belongs to 15-family is added to the Ni addition regions 506a and 506b, while leaving the protective film 504 as a mask. Regions 508a and 508b (hereinafter, designated as phosphorus addition region) to which phosphorus was added at high concentration are thus formed. [0151] Thereafter, heat processing at 600° C. for 12 hours is performed in an inert atmosphere as shown in FIG. 5(C). Ni existing in the polysilicon film 507 is moved by this heat processing, and almost all of them are finally captured by the

phosphorus addition regions **508***a* and **508***b* as shown by the arrow. It is thought that this is a phenomenon caused by the gettering effect of a metallic element (Ni in this embodiment) by phosphorus.

[0152] By this process, the concentration of Ni remaining in the polysilicon film 509 is reduced to at least  $2 \times 10^{17}$  atoms/cm³ according to the measurement value by SIMS (mass secondary ion analysis). Although Ni is a lifetime killer for a semiconductor, no adverse influence is given to the TFT characteristic when it is decreased to this extent Additionally, since this concentration is the measurement limit of the SIMS analysis in the current state of the art, it will show an even lower concentration (less than  $2 \times 10^{17}$  atoms/cm³) in practice. [0153] The polysilicon film 509 can be thus obtained that is crystallized by a catalyst and is decreased to the level in which

the catalyst does not obstruct the operation of a TFT. Thereafter, active layers **510-513** that use the polysilicon film **509** only are formed by a patterning process. At this time, a marker to conduct mask alignment in the following patterning should be formed by using the above polysilicon film. (FIG. **5**(D)) **[0154]** Thereafter, a silicon nitride oxide film 50 nm thick is formed by the plasma CVD method as shown in FIG. **5**(E), heating processing at 950° C. for 1 hour is then performed in an oxidation atmosphere, and a thermal oxidation process is performed. The oxidation atmosphere can be an oxygen atmosphere or another oxygen atmosphere in which halogen is added.

[0155] In this thermal oxidation process, the oxidation progresses in the interface between the active layer and the silicon nitride oxide film, and a polysilicon film whose thickness is about 15 nm is oxidized, so that a silicon oxide film whose thickness is about 30 nm is formed. That is, a gate insulating film 514 of a thickness of 80 nm is formed in which the silicon oxide film 30 nm thick and the silicon nitride oxide film 50 nm thick are laminated. The film thickness of the active layers 510-513 is made 30 nm by the thermal oxidation process.

[0156] Thereafter, as shown in FIG. 6(A), a resist mask 515 is formed, and an impurity element (hereinafter, designated as p-type impurity element) that gives the p-type through the medium of the gate insulating film 514 is added. As the p-type impurity element, an element that belongs to 13-family representatively, boron or gallium typically, can be used. This (called a channel dope process) is a process for controlling the threshold voltage of a TFT.

[0157] In this embodiment, boron is added by the ion dope method in which plasma excitation is performed without the mass separation of diborane ( $B_2H_6$ ). The ion implantation method that performs the mass separation can be used, of course. According to this process, impurity regions 516-518 are formed that include boron at the concentration of  $1\times10^{15}$ - $1\times10^{18}$  atoms/cm<sup>3</sup> ( $5\times10^{16}$ - $5\times10^{17}$  atoms/cm<sup>3</sup> representatively).

[0158] Thereafter, resist masks 519a and 519b are formed as shown in FIG. **6**(B), and an impurity element (hereinafter, designated as n-type impurity element) that gives the n-type through the medium of the gate insulating film **514** is added. As the n-type impurity element, an element that belongs to 15-family representatively, phosphorus or arsenic typically, can be used. In this embodiment, a plasma doping method in which plasma excitation is performed without the mass separation of phosphine (PH<sub>3</sub>) is used. Phosphorus is added in the concentration of  $1 \times 10^{18}$  atoms/cm<sup>3</sup>. The ion implantation method that performs mass separation can be used, of course. [0159] A dose amount is adjusted so that the n-type impurity element is included in the n-type impurity element is included in the n-type impurity regions 520, 521 formed by this process at the concentration of  $2 \times 10^{16}$ -5×  $10^{19}$  atoms/cm<sup>3</sup> ( $5 \times 10^{17}$ - $5 \times 10^{18}$  atoms/cm<sup>3</sup> representatively).

[0160] Thereafter, a process is performed for activating the added n-type impurity element and the added p-type, impurity element as shown in FIG. 6(C). There is no need to limit the activation means, but, since the gate insulating film 514 is disposed, the furnace annealing process that uses an electrothermal furnace is desirable. Additionally, it is preferable to perform heat processing at a temperature as high as possible because there is a possibility of having damaged the interface between the active layer and the gate insulating film of a part that is a channel formation region in the process of FIG. 6(A).

[0161] Since the crystallization glass with high heat resistance is used in this embodiment, the activating process is performed by the furnace annealing processing at 800° C. for 1 hour. The thermal oxidation can be performed keeping a processing atmosphere in an oxidizing atmosphere, or the heat processing can be performed in an inert atmosphere. However, the activating process is not indispensable.

[0162] This process clarifies the edge of the n-type impurity regions 520, 521, namely, the boundary (junction) between the n-type impurity regions 520, 521 and the region (p-type impurity region formed by the process of FIG. 6(A)) around the n-type impurity regions 520, 521, where the n-type impurity element is not added. This means that the LDD region and the channel formation region can form an excellent junction when a TFT is later completed.

**[0163]** Thereafter, a conductive film 200-400 nm thick is formed, and patterning is performed, so that gate electrodes **522-525** are formed. The gate electrode can be made of a conductive film of a single-layer, however, preferably, a lamination film, such as two-layer or three-layer film, is used when necessary. A known conductive film can be used as the material of the gate electrode.

[0164] Specifically, use can be made of a film of an element selected from the group consisting of tantalum (Ta), titanium (Ti), molybdenum (Mo), tungsten (W), chrome (Cr), and silicon (Si) having conductivity; a film of a nitride of the aforementioned elements (tantalum nitride film, tungsten nitride film, or titanium nitride film representatively); an alloy film of a combination of the aforementioned elements (Mo—W alloy or Mo—Ta alloy representatively); or, a silicide film of the aforementioned elements (tungsten silicide film or titanium silicide film representatively). They can have a single-layer structure or a lamination-layer structure, of course

[0165] In this embodiment, a lamination film is used that is made of a tungsten nitride (WN) film 50 nm thick and a tungsten (W) film 350 nm thick. This can be formed by the sputtering method. By adding an inert gas, such as Xe or Ne, as a spattering gas, the film can be prevented from peeling off because of stress.

[0166] At this time, the gate electrodes 523, 525 are formed to overlap with part of the n-type impurity regions 520, 521, respectively, with the gate insulating film 514 therebetween. The overlapping part is later made an LDD region overlapping with the gate electrode. According to the sectional view of the figure, the gate electrodes 524a and 524b are seen as separate, in fact, they are connected electrically to each other.

[0167] Thereafter, with the gate electrodes 522-525 as masks, an n-type impurity element (phosphorus in this embodiment) is added self-adjustably, as shown in FIG. 7(A). At this time, an adjustment is performed so that phosphorus is added to the thus formed impurity regions 526-532 at the concentration of  $\frac{1}{2}$ - $\frac{1}{10}$  ( $\frac{1}{3}$ - $\frac{1}{4}$  representatively) of that of the n-type impurity regions 520, 521. Preferably, the concentration is  $1\times10^{16}$ - $5\times10^{18}$  atoms/cm<sup>3</sup> ( $3\times10^{17}$ - $3\times10^{18}$  atoms/cm<sup>3</sup> typically).

[0168] Thereafter, as shown in FIG. 7(B), resist masks 533a-533d are formed to cover the gate electrode, an n-type impurity element (phosphorus in this embodiment) is then added, and impurity regions 534-540 including a high concentration of phosphorus are formed. The ion dope method using phosphine (PH<sub>3</sub>) is applied also herein, and an adjust-

ment is performed so that the concentration of phosphorus in these regions is  $1\times10^{20}$ - $1\times10^{21}$  atoms/cm<sup>3</sup> ( $2\times10^{20}$ - $5\times10^{20}$  atoms/cm<sup>3</sup> representatively).

**[0169]** A source region or a drain region of the n-channel type TFT is formed through this process, and the switching TFT leaves a part of the n-type impurity regions **529-531** formed in the process of FIG. **7**(A). The left region corresponds to the LDD regions **15***a***-15***d* of the switching TFT of FIG. **2**.

[0170] Thereafter, as shown in FIG. 7(C), the resist masks 533a-533d are removed, and a resist mask 541 is newly formed. A p-type impurity element (boron in this embodiment) is then added, and impurity regions 542, 543 including a high concentration of boron are formed. Herein, according to the ion dope method using diborane (B<sub>2</sub>H<sub>6</sub>), boron is added to obtain a concentration of  $3\times10^{20}$ - $3\times10^{21}$  atoms/cm<sup>3</sup> ( $5\times10^{20}$ - $1\times10^{21}$  atoms/cm<sup>3</sup> representatively).

[0171] Phosphorus has been already added to the impurity regions 542, 543 at a concentration of  $1\times10^{20}$ - $1\times10^{21}$  atoms/cm<sup>3</sup>. Boron added herein has at least three times as high concentration as the added phosphorus. Therefore, the impurity region of the n-type formed beforehand is completely changed into that of the p-type, and functions as an impurity region of the p-type.

[0172] Thereafter, as shown in FIG. 7(D), the resist mask 541 is removed, and then a first interlayer insulating film 544 is formed. As the first interlayer insulating film 544, an insulating film that includes silicon is used in the form of a single-layer structure or a stacked-layer structure as a combination thereof. Preferably, the film thickness thereof is 400 nm-1.5  $\mu$ m. In this embodiment, a structure is created in which an 800 nm-thick silicon oxide film is stacked on a 200 nm-thick silicon nitride oxide film.

**[0173]** Thereafter, the n-type or p-type impurity element added at each concentration is activated. The furnace annealing method is desirable as an activation means. In this embodiment, heat treatment is performed at 550° C. for 4 hours in a nitrogen atmosphere in an electrothermal furnace.

[0174] Heat treatment is further performed at 300-450° C. for 1-12 hours in an atmosphere that includes hydrogen of 3-100% for hydrogenation. This is a process to hydrogenterminate an unpaired connector of a semiconductor film by thermally excited hydrogen. As another means for hydrogenation, plasma hydrogenation (hydrogen excited by plasma is used) can be performed.

[0175] Hydrogenation can be performed during the formation of the first interlayer insulating film 544. In more detail, the 200 nm-thick silicon nitride oxide film is formed, and hydrogenation is performed as mentioned above, and thereafter the remaining 800 nm-thick silicon oxide film can be formed.

[0176] Thereafter, as shown in FIG. 8(A), contact holes are made in the first interlayer insulating film 544, and source wiring lines 545-548 and drain wiring lines 549-551 are formed. In this embodiment, this electrode is formed with a lamination film of a three-layer structure in which a 100 nm-thick Ti film, a 300 nm-thick aluminum film that includes Ti, and a 150 nm-thick Ti film are continuously formed according to the sputtering method. Other conductive films can be used, of course.

[0177] Thereafter, a first passivation film 552 is formed to be 50-500 nm thick (200-300 nm thick representatively). In

this embodiment, a 300 nm-thick silicon nitride oxide film is used as the first passivation film **552**. A silicon nitride film can be substituted for this.

[0178] At this time, it is effective to perform plasma treatment by the use of gas that includes hydrogen, such as  $\rm H_2$  or  $\rm NH_3$ , prior to the formation of the silicon nitride oxide film. Hydrogen excited by this preprocess is supplied to the first interlayer insulating film **544**, and, through heat treatment, the film quality of the first passivation film **552** is improved. At the same time, since hydrogen that is added to the first interlayer insulating film **544** diffuses onto the lower side, the active layer can be effectively hydrogenated.

[0179] Thereafter, as shown in FIG. 8(B), a second interlayer insulating film 553 made of organic resin is formed. Polyimide, acrylic fiber, or BCB (benzocyclobutene) can be used as the organic resin. Especially, since the second interlayer insulating film 553 is required to flatten the level differences formed by TFTs, an acrylic film excellent in smoothness is desirable. An acrylic film is formed to be 2.5  $\mu$ m thick in this embodiment.

[0180] Thereafter, contact holes that reach the drain wiring line 551 are made in the second interlayer insulating film 553 and the first passivation film 552, and a pixel electrode 554 (anode) is formed. In this embodiment, an indium oxide/tin (ITO) film is formed to be 110 nm thick, and it is made a pixel electrode by patterning. A transparent conductive film can be used in which zinc oxide (ZnO) of 2-20% is mixed with indium oxide. This pixel electrode functions as the anode of the EL element.

[0181] Thereafter, an insulating film (a silicon oxide film in this embodiment) that includes silicon is formed to be 500 nm thick, an opening is then formed at the position corresponding to the pixel electrode 554, and a third interlayer insulating film 555 is formed. It is possible to easily form a tapered sidewall by using the wet etching method when the opening is formed. If the sidewall of the opening does not have a sufficiently gentle slope, deterioration of the EL layer caused by level differences will lead to an important problem.

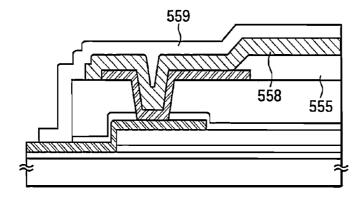

[0182] Thereafter, an EL layer 556 and a cathode (MgAg electrode) 557 are continuously formed without air exposure by the vacuum deposition method. Preferably, the film thickness of the EL layer 556 is 800-200 nm (100-200 nm typically), and that of the cathode 557 is 180-300 nm (200-250 nm typically).

**[0183]** In this process, an EL layer and a cathode are sequentially formed for a pixel corresponding to red, a pixel corresponding to green, and a pixel corresponding to blue. However, since the EL layer is poor in tolerance to solutions, they must be independently formed for each color without using the photolithography technique. Thus, it is preferable to conceal pixels except a desired one by the use of the metal mask, and selectively form an EL layer and a cathode for the desired pixel.

[0184] In detail, a mask is first set for concealing all pixels except a pixel corresponding to red, and an EL layer and a cathode of red luminescence are selectively formed by the mask. Thereafter, a mask is set for concealing all pixels except a pixel corresponding to green, and an EL layer and a cathode of green luminescence are selectively formed by the mask. Thereafter, as above, a mask is set for concealing all pixels except a pixel corresponding to blue, and an EL layer and a cathode of blue luminescence are selectively formed by the mask. In this case, the different masks are used for the respective colors. Instead, the same mask may be used for

them. Preferably, processing is performed without breaking the vacuum until the EL layer and the cathode are formed for all the pixels.

[0185] A known material can be used for the EL layer 556. Preferably, that is an organic material in consideration of driving voltage. For example, the EL layer can be formed with a four-layer structure consisting of a positive hole injection layer, a positive hole transporting layer, a luminescent layer, and an electronic injection layer. The MgAg electrode is used as the cathode of the EL element in this embodiment. Known other materials can be used instead of it.

[0186] As the protective electrode 558, a conductive film largely composed of aluminum can be used. The protective electrode 558 can be formed according to the vacuum deposition method by using a mask different from the mask when the EL layer and the cathode are formed. Preferably, it is continuously formed without air exposure after the EL layer and the cathode are formed.

[0187] At the final stage, a second passivation film 559 made of a silicon nitride film is formed to be 300 nm thick. In practice, the protective electrode 558 functions to protect the EL layer from, for example, water. In addition, the reliability of the EL element can be further improved by forming the second passivation film 559.

[0188] An active matrix type EL display device constructed as shown in FIG. 8(C) is completed. In practice, preferably, the device is packaged (sealed) by a highly airtight protective film (laminate film, ultraviolet cured resin film, etc.) or a housing material such as a ceramic sealing can, in order not to be exposed to the air when completed as shown in FIG. 8(C). In that situation, the reliability (life) of the EL layer is improved by making the inside of the housing material an inert atmosphere or by placing a hygroscopic material (for example, barium oxide) therein.

[0189] After airtightness is improved by, for example, packaging, a connector (flexible print circuit: FPC) for connecting a terminal drawn from the element or circuit formed on the substrate to an external signal terminal is attached, and a product is completed. In this specification, the EL display device, thus wholly prepared for market, is called EL module.

[0190] Now, the structure of the active matrix type EL display device of this embodiment will be described with reference to the perspective view of FIG. 11. The active matrix type EL display device of this embodiment is made up of a pixel portion 602, a gate signal side driving circuit 603, and a data signal side driving circuit 604, each formed on a glass substrate 601. A switching TFT 605 of the pixel portion is an n-channel type TFT, and is disposed at the intersection of a gate wiring line 606 connected to the gate signal side driving circuit 603 and a source wiring line 607 connected to the data signal side driving circuit 604. The drain of the switching TFT 605 is connected to the gate of a current controlling TFT 608.

[0191] The source of the current controlling TFT 608 is connected to a current-feed line 609, and the drain of the current controlling TFT 608 is connected to an EL element 610. A predetermined voltage is applied to the cathode of the EL element 610.

[0192] A FPC 611 which is an external input-output terminal is provided with input wiring lines (connection wiring lines) 612, 613 for transmitting a signal to the driving circuit, and an input wiring line 614 connected to the current-feed line 609.

[0193] The EL module of this embodiment including housing materials will now be described with reference to FIGS. 12(A) and 12(B). Reference characters used in FIG. 11 are again used when necessary.

[0194] A pixel portion 1201, a data signal side driving circuit 1202, and a gate signal side driving circuit 1203 are formed on a substrate 1200. Various wiring lines from each driving circuit are connected to external equipment via the input wiring lines 612-614 and the FPC 611.